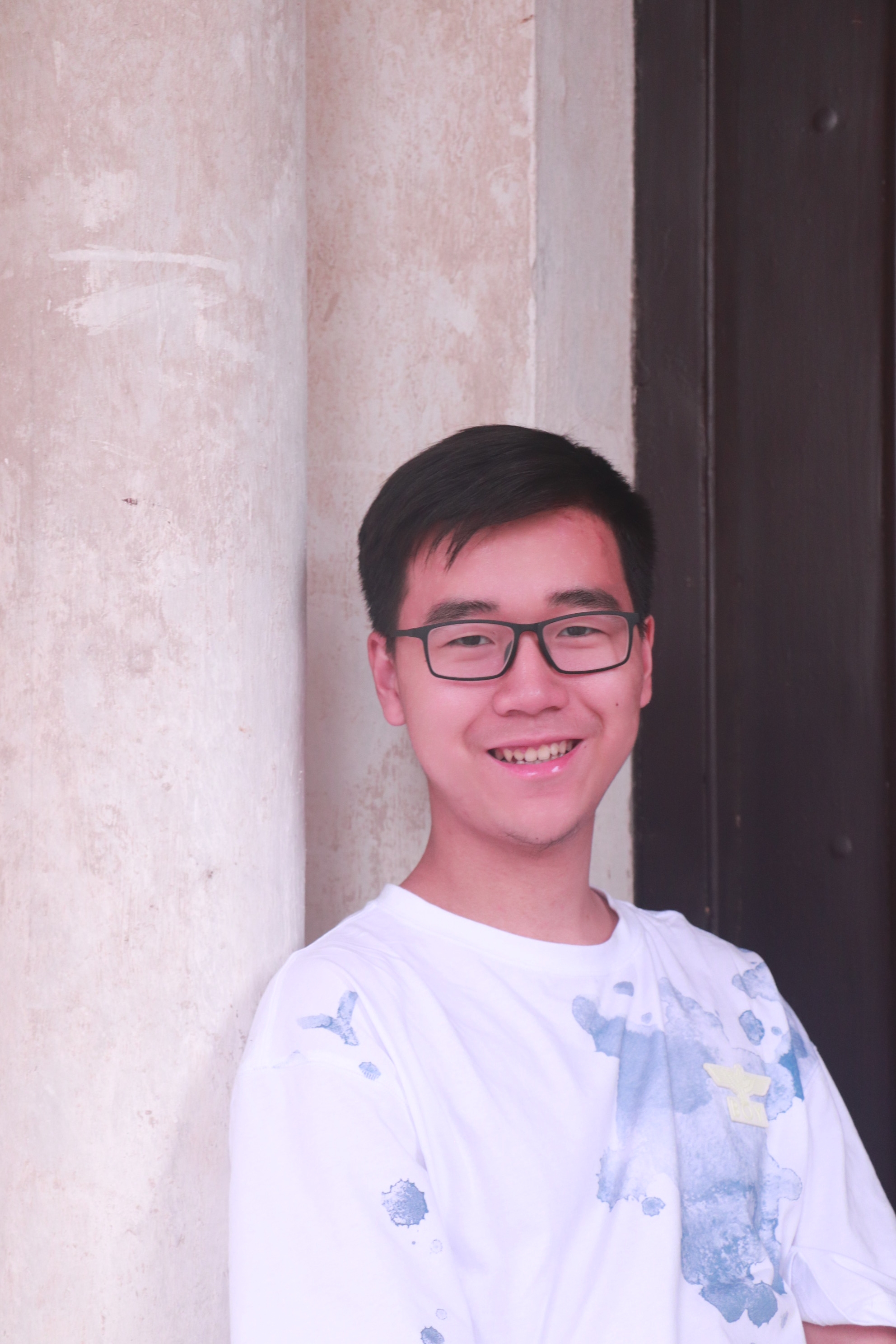

Yichuan Wang

Bio

I am a first-year PhD student at UC Berkeley in SkyLab and received my B.E. in Computer Science and Technology from ACM Honored Class, Shanghai Jiao Tong University(SJTU). I am interested in machine learning systems and high-performance computing systems particularly in distributed systems for large ML model training/serving and developing tailored abstractions for unique ML computational patterns to enhance performance. To be more specific, currently, I am more interested in LLM serving/scheduling, multi-agent systems, large scale RAG and GraphRAG. If you share similar interests, I'd love to chat.

Previously, I collaborated with Prof.Jinyang Li in NYU and Dr.Minjie Wang on a project related to scaling up GNN training. In SJTU, I am supervised by Prof. Quan Chen at EPCC. I like to communicate with different people, so you can feel free to contact me via email wechat:15858459091 or yichuanwang0324 or twitter If you are willing to know more details, you can see my CV here. If you are interested in my motivation, you can also look at my SoP for application.

In my spare time, I have also contributed to open-source projects, like SGLang recently.

Work Email: yichuan_wang@berkeley.edu

Personal Email: yichuanmistygrass@gmail.com

News

[06/20/2025] I will attend SIGMOD in Berlin this year. Let's chat about vector database, RAG, LLM and we can hang around!

[08/29/2024] After being rejected once, DiskGNN has finally been accepted by SIGMOD25. See you in Berlin!

[08/13/2024] Starting my PhD journey at SkyLab—excited.

[05/08/2024] We put DiskGNN on Arxiv If you want to train a super-large-scale GNN while balancing speed and accuracy, you should try it! We will integrate it into DGL asap.

Education

UC Berkeley

Starting from Sept. 2024

PhD in EECS

Shanghai Jiao Tong University

Sept. 2020 -- June 2024

B.Eng. in Computer Science at ACM Honors Class, advised by Prof. Quan Chen, Prof. Yong Yu

New York University Courant Institute

July. 2023 -- Dec. 2023

Research assistant, advised by Prof. Jinyang Li

Publications

1.LEANN: A Low-Storage Vector Index pdf

Yichuan Wang, Shu Liu, Zhifei Li, Yongji Wu, Ziming Mao, Yilong Zhao, Xiao Yan, Zhiying Xu, Yang Zhou, Ion Stoica, Sewon Min, Matei Zaharia, Joseph E. Gonzalez

Preprint (Short version in VecDB@ICML2025)

2.Locality-aware Fair Scheduling in LLM Serving pdf

Shiyi Cao*, Yichuan Wang*, Ziming Mao, Pin-Lun Hsu, Liangsheng Yin, Tian Xia, Dacheng Li, Shu Liu, Yineng Zhang, Yang Zhou, Ying Sheng, Joseph E. Gonzalez, Ion Stoica

*indicates equal contribution

Preprint

3.DiskGNN: Bridging I/O Efficiency and Model Accuracy for Out-of-Core GNN Training pdf

Renjie Liu*, Yichuan Wang*, Xiao Yan, Zhenkun Cai, Minjie Wang, Haitian Jiang, Bo Tang, Jinyang Li

*indicates equal contribution

Accepted by SIGMOD 2025

4.Optimizing Dynamic Neural Networks with Brainstorm pdf

Weihao Cui, Zhenhua Han, Lingji Ouyang, Yichuan Wang, Ningxin Zheng, Lingxiao Ma, Yuqing Yang, Fan Yang, Jilong Xue, Lili Qiu, Lidong Zhou, Quan Chen, Haisheng Tan, Minyi Guo.

Accepted by OSDI 2023

5.Forming Scalable, Convergent GNN Layers that Minimize a Sampling-Based Energy pdf

Haitian Jiang, Renjie Liu, Zengfeng Huang, Yichuan Wang, Xiao Yan, Zhenkun Cai, Minjie Wang, David Wipf

Accepted by ICLR 2025

6.The Danger of Overthinking: Examining the Reasoning-Action Dilemma in Agentic Tasks pdf

Alejandro Cuadron, Dacheng Li, Wenjie Ma, Xingyao Wang, Yichuan Wang, Siyuan Zhuang, Shu Liu, Luis Gaspar Schroeder, Tian Xia, Huanzhi Mao, Nicholas Thumiger, Aditya Desai, Ion Stoica, Ana Klimovic, Graham Neubig, Joseph E. Gonzalez

Preprint

7.Autellix: An Efficient Serving Engine for LLM Agents as General Programs pdf

Michael Luo, Xiaoxiang Shi, Colin Cai, Tianjun Zhang, Justin Wong, Yichuan Wang, Chi Wang, Yanping Huang, Zhifeng Chen, Joseph E. Gonzalez, Ion Stoica

Accepted by NSDI 2026

Services

- [04/2025] SIGMOD'25 Artifact Evaluation Committee

- [03/2025] MLsys'25 Artifact Evaluation Committee

- [02/2025] Eurosys'25 Artifact Evaluation Committee

- [07/2024] SIGCOMM'24 Artifact Evaluation Committee

- [04/2024] OSDI'24 Artifact Evaluation Committee

- [04/2024] USENIX ATC'24 Artifact Evaluation Committee

Misc/Hobbies

I like playing basketball! (But unfortunately, it seems that there aren't any good basketball courts near Berkeley.) So now, I might (or rather, I can only) play more badminton(I still enjoy). Besides that, I've been an NBA fan for 15 years, and I like Chris Paul! In recent years, I've also become very interested in the Premier League(I love Manchester City, come on Blue Moon!). If you share the same interests, we should chat/hang out!

Blog Posts

Here are my thoughts and comments on various research papers and topics in systems and ML:

Paper Comments

- My Thoughts on RAGCache paper - My thoughts on RAGCache paper arxiv

- My Thoughts on Exploring Orak: A Unified Benchmark for LLM Agents in Games paper - My thoughts on Orak paper, a comprehensive evaluation on Game Plantform arxiv